# MSP58C80/C81/C82 Mixed-Signal Processor

## User's Guide

## MSP58C80/C81/C82 Mixed-Signal Processor User's Guide

July 1996 SPSU005B

#### IMPORTANT NOTICE

Texas Instruments (TI) reserves the right to make changes to its products or to discontinue any semiconductor product or service without notice, and advises its customers to obtain the latest version of relevant information to verify, before placing orders, that the information being relied on is current.

TI warrants performance of its semiconductor products and related software to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

Certain applications using semiconductor products may involve potential risks of death, personal injury, or severe property or environmental damage ("Critical Applications").

TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, INTENDED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT APPLICATIONS, DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS.

Inclusion of TI products in such applications is understood to be fully at the risk of the customer. Use of TI products in such applications requires the written approval of an appropriate TI officer. Questions concerning potential risk applications should be directed to TI through a local SC sales office.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards should be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance, customer product design, software performance, or infringement of patents or services described herein. Nor does TI warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used.

Copyright © 1996, Texas Instruments Incorporated

Printed in U.S.A. by Great Impressions Printing & Graphics Dallas, Texas

### **Preface**

### **Read This First**

### About This Manual

This user's guide serves as a reference book for the MSP58C80/C81/C82 mixed-signal processor and is used in conjunction with the *TMS320C2x User's Guide*.

Related documentation is listed on page v.

This document contains the following chapters:

### How to Use This Manual

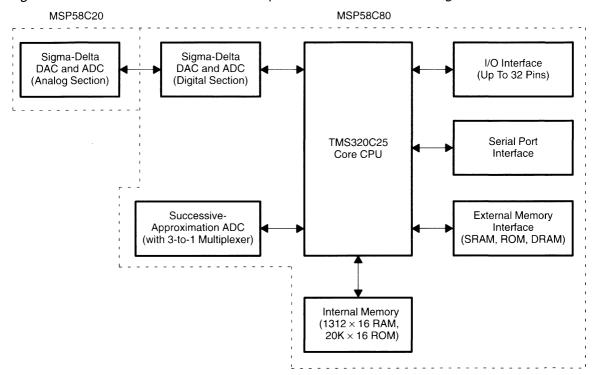

| <b>Chapter 1</b> describes the design of the MSP58C80. This description includes a list of possible applications, a functional block diagram, a list of features, a pinout, signal descriptions, and a list of differences from the TMS320C25.                                                                                                                                                                        |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Chapter 2</b> describes the architecture of the MSP58C80. The memory organization is discussed in detail including program memory, data memory, memory maps, memory-mapped registers, I/O-mapped registers, alternate data space, interfacing to standard memory, and interfacing to DRAM. Interrupts, analog-to-digital converters, digital-to-analog converters, and low-power operation finish out the chapter. |

gramming memory-mapped registers.

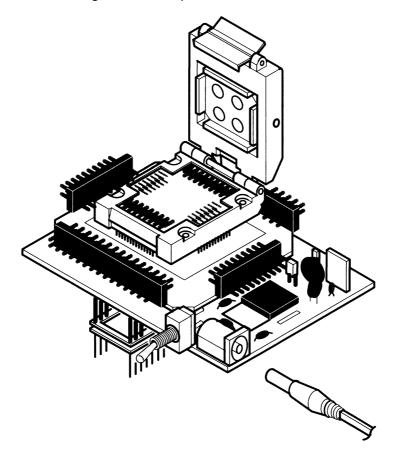

Chapter 4 describes the EVM58C80 development tool and related equipment. This chapter contains a discussion of the EVM58C80 development

☐ Chapter 3 describes application information needed for the MSP58C80. This includes a software overview, the reset circuit, interrupts, and pro-

- tool, hardware connection and setup, monitor-mode commands, and debug-mode commands.

- ☐ Chapter 5 contains a list of frequently asked questions as compiled by TI's application staff. The questions range from MSP58C80 functionality to application information.

|                        | <b>Appendix A</b> contains program code for a simple program. It also contains a list of DOS commands for assembling and linking, a step-by-step list for setting up the EVM58C80 hardware and executing a simple program, and an explanation of how to upgrade the EVM system software.                       |  |  |  |

|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|                        | <b>Appendix B</b> contains the electrical specifications and timings for the MSP58C80/C81/C82.                                                                                                                                                                                                                 |  |  |  |

|                        | <b>Appendix C</b> describes the results of different MEMTYPE and FREQ memory-mapped register setups and the resulting MSP58C80 functional stability.                                                                                                                                                           |  |  |  |

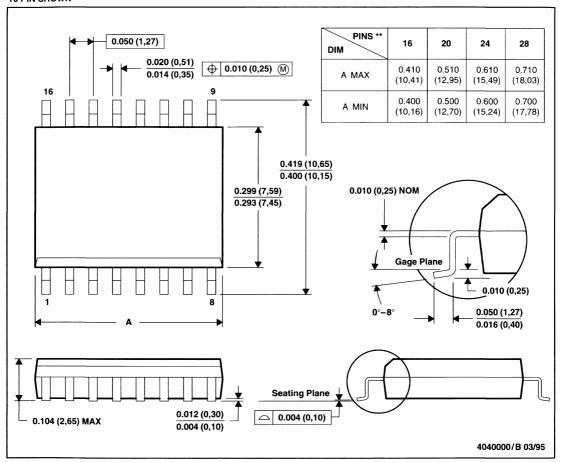

|                        | <b>Appendix D</b> contains customer information including an example of a new product release form and mechanical information.                                                                                                                                                                                 |  |  |  |

|                        | Appendix E contains a copy of the MSP58C20 data sheet.                                                                                                                                                                                                                                                         |  |  |  |

|                        | <b>Appendix F</b> contains information on programming the MSP58P80/P81. The MSP58P80/P81 incorporates a one-time programmable (OTP) 32K $\times$ 16-bit EPROM designed to function as a 64K $\times$ 8-bit EPROM (TMS27PC512) when used with a programmer adapter.                                             |  |  |  |

|                        | <b>Appendix G</b> describes the differences of the MSP58C81/C82 from the MSP58C80. This description includes a functional block diagram, a list of features, a pinout, signal descriptions, differences in memory-mapped registers, differences in I/O-mapped registers, and differences in development tools. |  |  |  |

|                        | <b>Appendix H</b> is a glossary that defines acronyms and key words used in this book.                                                                                                                                                                                                                         |  |  |  |

| Notational Conventions | 5                                                                                                                                                                                                                                                                                                              |  |  |  |

| Thi                    | This document uses the following conventions:                                                                                                                                                                                                                                                                  |  |  |  |

|                        | Program listings, program examples, and interactive displays are shown in a special typeface similar to that of a typewriter.                                                                                                                                                                                  |  |  |  |

|                        | Here is a sample program listing:                                                                                                                                                                                                                                                                              |  |  |  |

|                        | 0011 0005 0001 .field 1, 2<br>0012 0005 0003 .field 3, 4<br>0013 0005 0006 .field 6, 3                                                                                                                                                                                                                         |  |  |  |

### Information About Cautions

This book may contain cautions and warnings.

This is an example of a caution statement.

A caution statement describes a situation that could potentially damage your software or equipment.

#### Related Documentation From Texas Instruments

The following book describes the TMS320C2x and related support tools. To obtain a copy of this TI document, call the Texas Instruments Literature Response Center at (800) 477–8924. When ordering, please identify the book by its title and literature number.

**TMS320C2x User's Guide** (SPRU014C) discusses the hardware aspects of the TMS320 family of 16-/32-bit single-chip digital signal processors. These processors combine the flexibility of a high-speed controller with the numerical capability of an array processor, offering an inexpensive alternative to custom VLSI and multichip bit-slice processors for signal processing.

### From Other Sources

EVEREADY™ Battery Engineering Data: Alkaline (Volume 2A), 1990.

### If You Need Assistance. . .

| If you want to                                                                                  | Do this                                                                                                                              |

|-------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| Request more information about<br>Texas Instruments Digital Signal<br>Processing (DSP) products | Write to: Texas Instruments Incorporated Market Communications Manager, MS 736 P.O. Box 1443 Houston, Texas 77251–1443               |

| Order Texas Instruments documentation                                                           | Call the TI Literature Response Center: (800) 477–8924                                                                               |

| Report mistakes in this document or any other TI documentation                                  | Send your comments to: Texas Instruments Incorporated Technical Publications Manager, MS 702 P.O. Box 1443 Houston, Texas 77251–1443 |

### **Trademarks**

Apple and Macintosh are trademarks of Apple Computer, Inc.

Data I/O and Chiplab are trademarks of the Data I/O Corporation.

EVEREADY is a trademark of the Eveready Battery Company Inc.

IBM PC and PC-AT are trademarks of International Business Machines Corp.

MS-DOS is a trademark of Microsoft Corp.

Procomm Plus is a trademark of DATASTORM TECHNOLOGIES, INC.

## **Contents**

| 1 | Intro | duction  | n to the MSP58C80                                   | 1-1  |

|---|-------|----------|-----------------------------------------------------|------|

|   | 1.1   | Introd   | luction                                             | 1-2  |

|   | 1.2   | Descr    | ription                                             | 1-4  |

|   | 1.3   | Featu    | res                                                 | 1-5  |

|   | 1.4   | Pinou    | It and Signal Descriptions                          | 1-7  |

|   | 1.5   | Differe  | ences Between the MSP58C80 and the TMS320C25        | 1-14 |

|   |       | 1.5.1    | Deletions                                           | 1-14 |

|   |       | 1.5.2    | Enhancements                                        | 1-15 |

| 2 | MSP   | 58C80 /  | Architecture                                        | 2-1  |

|   | 2.1   |          | ory Organization                                    | 2-2  |

|   |       | 2.1.1    | Program and Data Memory                             | 2-2  |

|   |       | 2.1.2    | Memory Maps                                         | 2-3  |

|   |       | 2.1.3    | Memory-Mapped Registers                             | 2-7  |

|   |       | 2.1.4    | I/O-Mapped Registers                                |      |

|   |       | 2.1.5    | Addressing the Alternate Data Space                 | 2-22 |

|   |       | 2.1.6    | Interfacing With Standard Memory                    |      |

|   |       | 2.1.7    | Interfacing With DRAM                               |      |

|   |       | 2.1.8    | Interfacing With External I/O Registers             |      |

|   | 2.2   |          | upts                                                |      |

|   |       | 2.2.1    | Reset Interrupt                                     |      |

|   | 2.3   |          | g and Digital Converters                            |      |

|   | 2.4   | Low-P    | Power Operation                                     | 2-44 |

| 3 |       |          | s                                                   |      |

|   | 3.1   |          | are Package                                         |      |

|   | 3.2   |          | Circuit and Interrupts                              |      |

|   | 3.3   | Progra   | amming the FREQ and MEMTYPE Memory-Mapped Registers | 3-4  |

| 4 |       |          | Development Tools                                   |      |

|   | 4.1   |          | 8C80 In-Circuit Emulator                            |      |

|   | 4.2   |          | 8C80 Monitor-Mode Commands                          |      |

|   | 4.3   | EVM5     | 8C80 Debug-Mode Commands                            | 4-14 |

| 5 | Frequ | uently A | Asked Questions                                     | 5-1  |

| Α | Asse        | mbly To Emulation With a Simple Program                                                   | A-1         |

|---|-------------|-------------------------------------------------------------------------------------------|-------------|

|   | A.1         | Simple Program                                                                            | A-2         |

|   | A.2         | Simple Linker File                                                                        | <b>A-</b> 3 |

|   | A.3         | MS-DOS Commands for Assembling and Linking                                                | A-4         |

|   | A.4         | Connecting the Hardware                                                                   | <b>A-</b> 5 |

|   | <b>A</b> .5 | Running the Program                                                                       |             |

|   | A.6         | Upgrading the EVM System Software                                                         | 8-A         |

| В | Elect       | rical Specifications and Timings                                                          | B-1         |

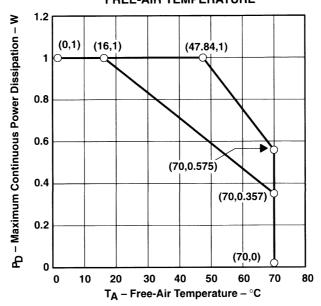

|   | B.1         | Absolute Maximum Ratings Over Operating Free-Air Temperature Range                        |             |

|   | B.2         | Recommended Operating Conditions                                                          |             |

|   | B.3         | Electrical Characteristics                                                                |             |

|   | B.4         | Clock and Timing Characteristics                                                          |             |

|   |             | B.4.1 Recommended Clock Operating Conditions                                              |             |

|   |             | B.4.2 DRAM Timing Requirements for the MSP58C80                                           | B-7         |

|   |             | B.4.3 Dynamic-Memory Switching Characteristics for the MSP58C80                           |             |

|   |             | B.4.4 SRAM Timing Characteristics for the MSP58C80                                        |             |

|   |             | B.4.5 RS and INTO Timing B                                                                |             |

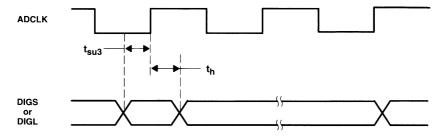

|   |             | B.4.6 Serial-Port Timing B                                                                | -12         |

| С | Mem         | ory-Mapped Register Constraints                                                           |             |

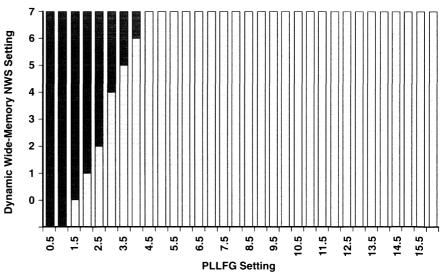

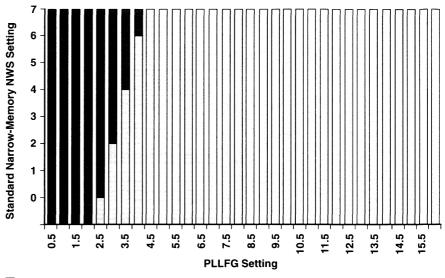

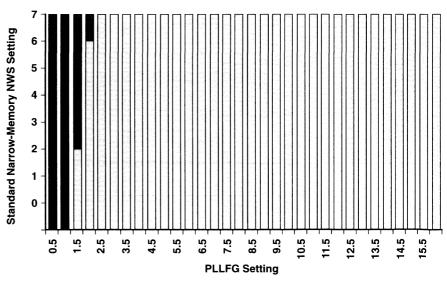

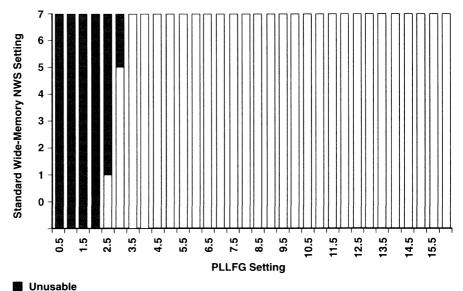

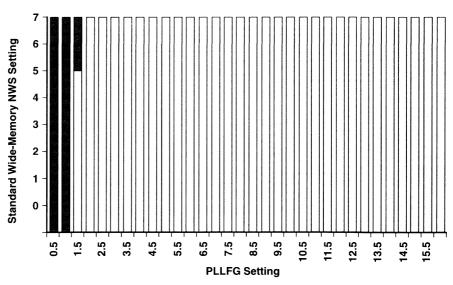

|   | C.1         | PLLFG and NWS Settings To Avoid If Refresh Is Enabled                                     |             |

|   | C.2         | PLLFG and PCPD Settings To Avoid If Refresh Is Enabled                                    | C-4         |

|   | C.3         | Settings To Avoid If Dynamic Memory Reads or Writes Are Performed and Refresh Is          |             |

|   | <b>~</b> 4  | Enabled                                                                                   |             |

|   | C.4         | Settings To Avoid If Standard Memory Reads or Writes Are Performed and Refresh Is Enabled | C-9         |

| D | Cuet        | omer Information                                                                          | D_1         |

| _ | D.1         | New Product Release Form for the MSP58C80                                                 |             |

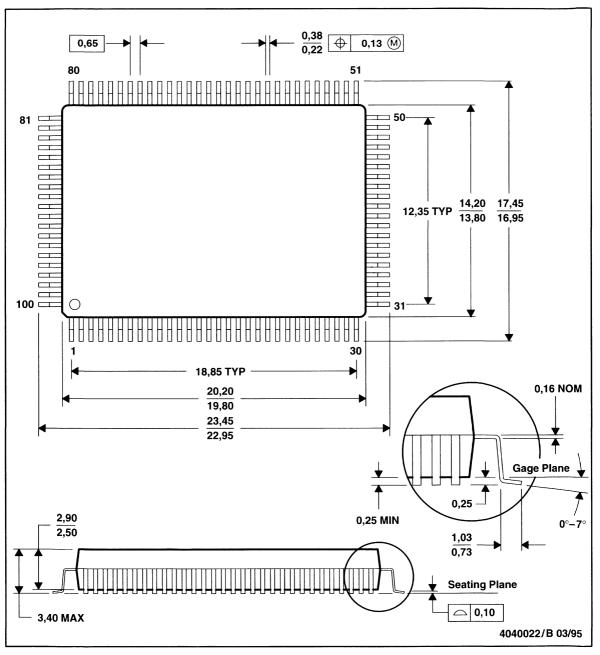

|   | D.2         | Mechanical Information                                                                    |             |

| _ |             |                                                                                           |             |

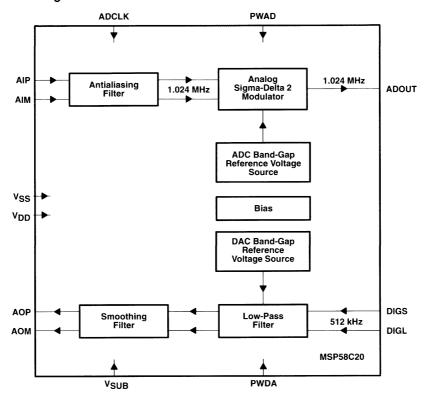

| Ε | MSP         | 58C20 Audio-Band Converter Data Sheet                                                     | E-1         |

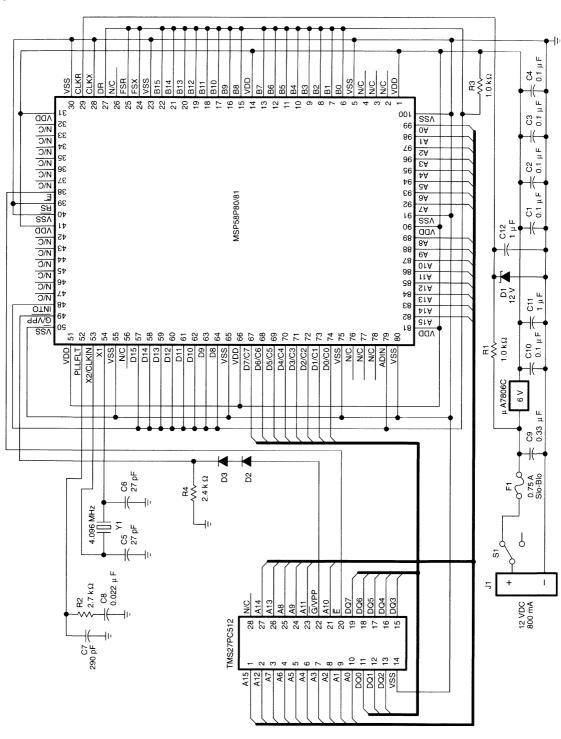

| F | MSP         | 58P80/P81 EPROM Programming                                                               |             |

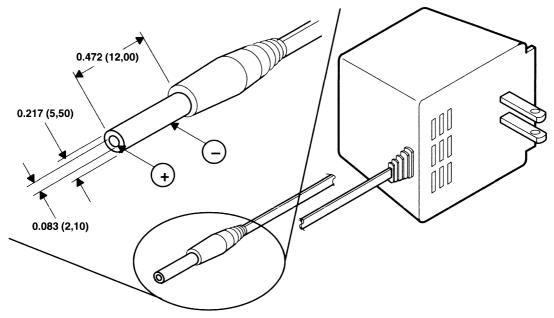

|   | F.1         | Using the EPROM Programmer Adapter Socket                                                 |             |

|   |             | F.1.1 Supplying External Power                                                            |             |

|   | F.2         | Programming and Verification                                                              |             |

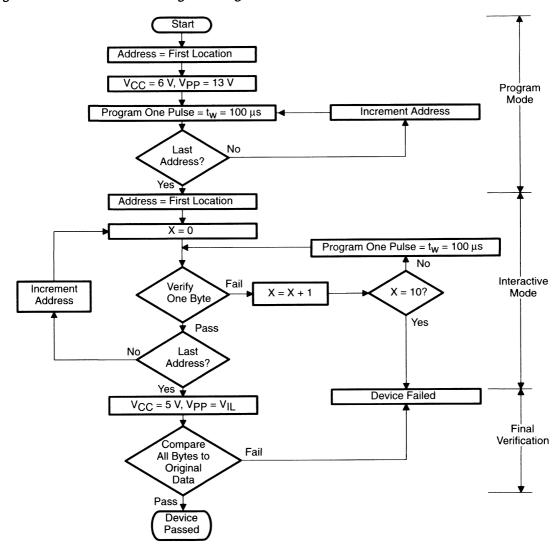

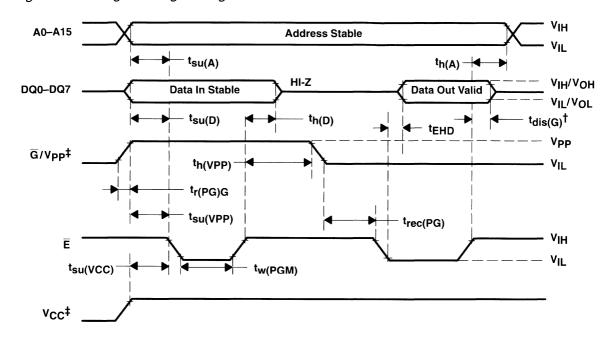

|   |             | F.2.1 SNAP! Pulse Programming                                                             |             |

|   |             | F.2.2 Program Verify                                                                      |             |

|   |             | F.2.3 Program Inhibit                                                                     |             |

|   |             | F.2.4 Read/Output Disable F                                                               |             |

|   |             | F.2.5 Standby F                                                                           |             |

|   | _           | F.2.6 Signature Mode F                                                                    |             |

|   | F3          | Step-By-Step Procedure                                                                    | -12         |

| G | MSP  | 58C81/C82 Mixed-Signal Processor | G-1    |

|---|------|----------------------------------|--------|

|   |      | Introduction                     |        |

|   | G.2  | Features                         | G-3    |

|   | G.3  | Pinout and Signal Descriptions   | G-5    |

|   |      | Memory Organization              |        |

|   |      | G.4.1 Memory-Mapped Registers    |        |

|   |      | G.4.2 I/O-Mapped Registers       | . G-13 |

|   | G.5  | Development Tools                | . G-15 |

| Н | Glos | sarv                             | H-1    |

## **Figures**

|      | AND THE PROPERTY OF THE PROPER |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

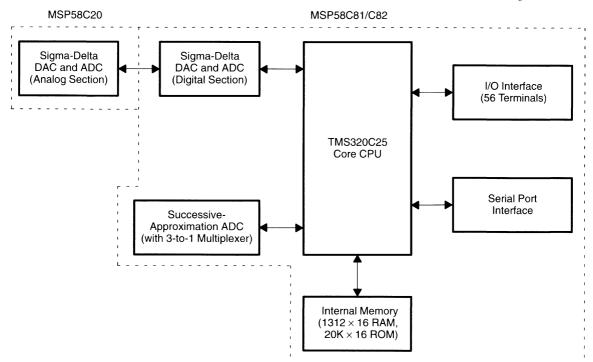

| 1–1  | MSP58C80/MSP58C20 Simplified Functional Block Diagram 1-4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

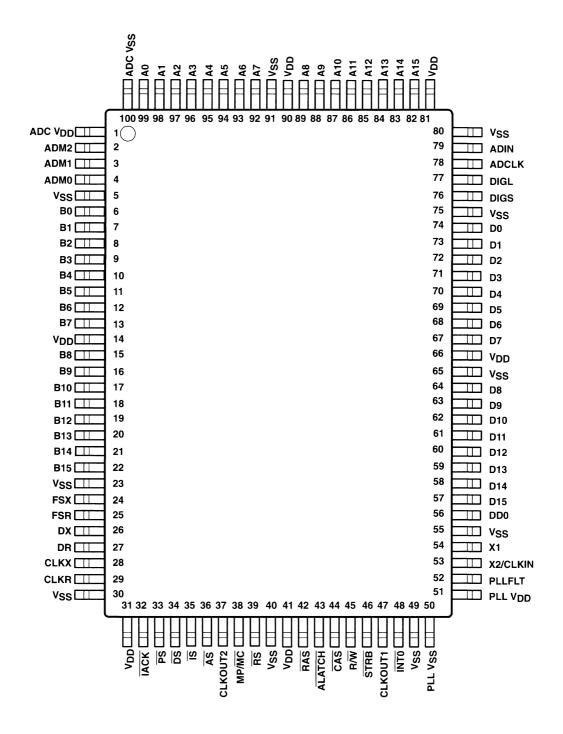

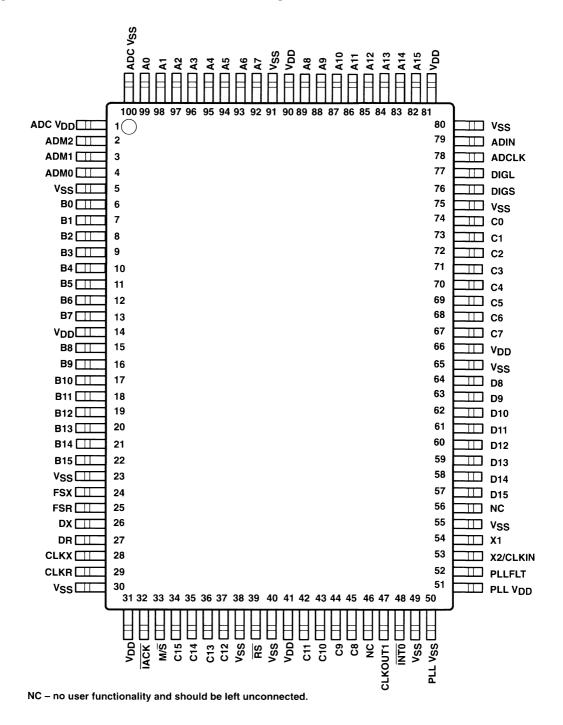

| 1–2  | MSP58C80 Terminal Assignments 1-8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

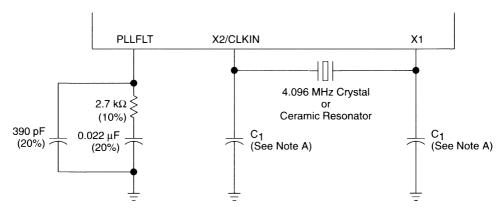

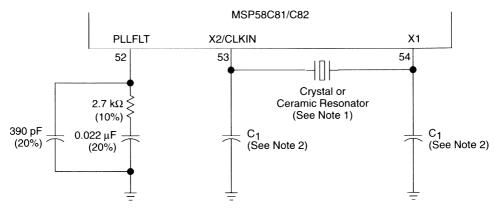

| 1–3  | External Clock and PLL Filter 1-9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

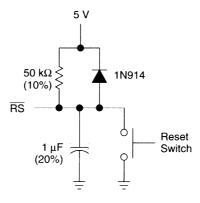

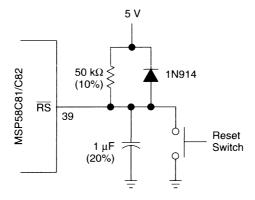

| 1–4  | Reset Circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

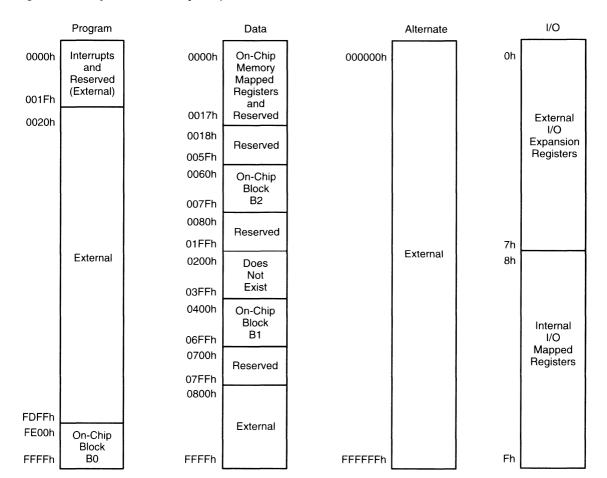

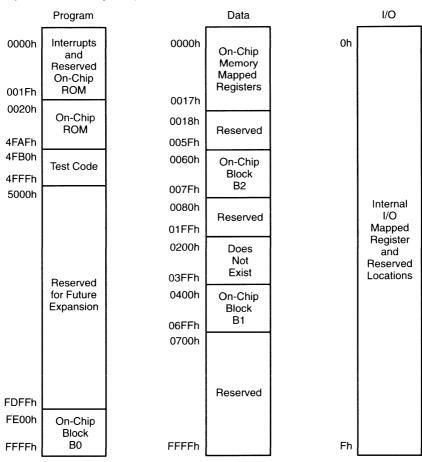

| 2–1  | System Memory Maps With MP/ $\overline{MC}$ = 0 After a CNFD Instruction 2-4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 2–2  | System Memory Maps With MP/MC = 0 After a CNFP Instruction 2-5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 2–3  | System Memory Maps With MP/MC = 1 After a CNFD Instruction 2-6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 2–4  | System Memory Maps With MP/MC = 1 After a CNFP Instruction 2-7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

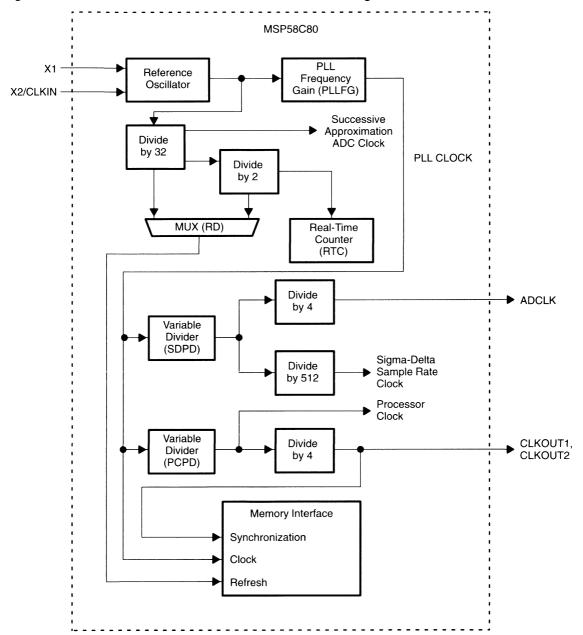

| 2–5  | Clock Generation and Distribution Block Diagram 2-15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

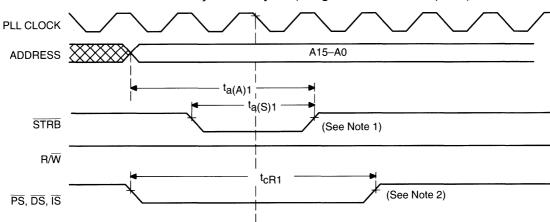

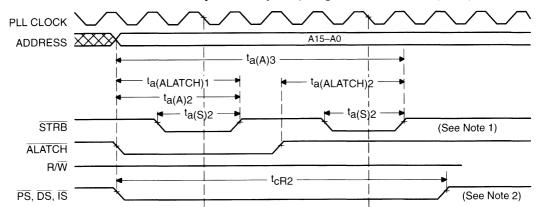

| 2–6  | Standard Wide-Memory Read Cycle (Program, Data, I/O Space) 2-26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

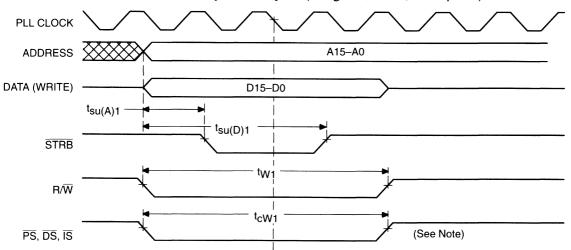

| 2–7  | Standard Wide-Memory Write Cycle (Program, Data, I/O Space) 2-27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

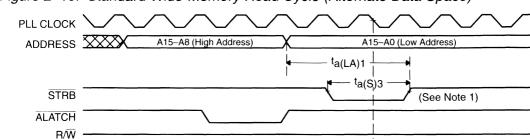

| 2–8  | Standard Narrow-Memory Read Cycle (Program, Data, I/O Space) 2-28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

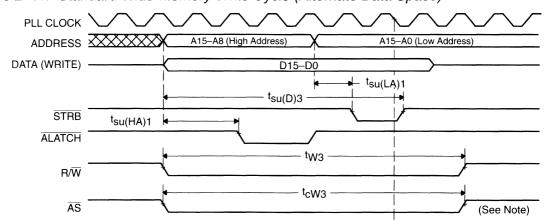

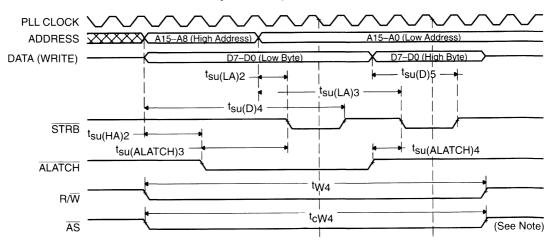

| 2–9  | Standard Narrow-Memory Write Cycle (Program, Data, I/O Space) 2-28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 2–10 | Standard Wide-Memory Read Cycle (Alternate Data Space) 2-29                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 2–11 | Standard Wide-Memory Write Cycle (Alternate Data Space) 2-29                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

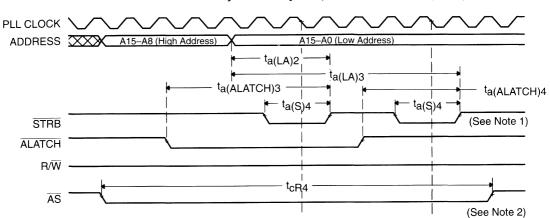

| 2–12 | Standard Narrow-Memory Read Cycle (Alternate Data Space) 2-30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 2–13 | Standard Narrow-Memory Write Cycle (Alternate Data Space) 2-30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

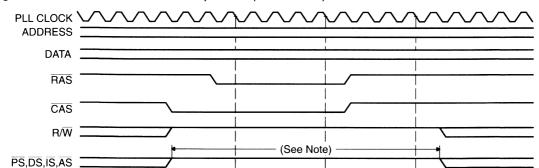

| 2–14 | 16-Bit DRAM-Memory Read Cycle Using 1-Bit Wide Memory 2-33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

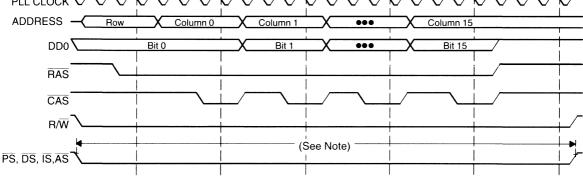

| 2–15 | 16-Bit DRAM Memory Write Cycle Using 1-Bit Wide Memory 2-33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

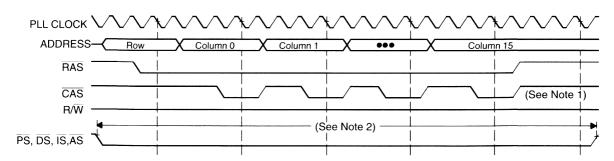

| 2–16 | 16-Bit DRAM Memory Read Cycle Using 4-Bit Wide Memory 2-34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 2–17 | 16-Bit DRAM Memory Write Cycle Using 4-Bit Wide Memory 2-34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

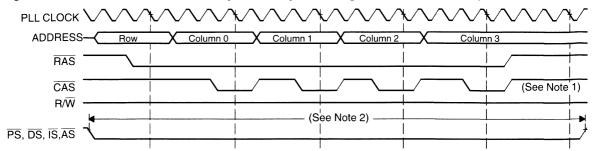

| 2–18 | DRAM Refresh Sequence (All Widths) 2-35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

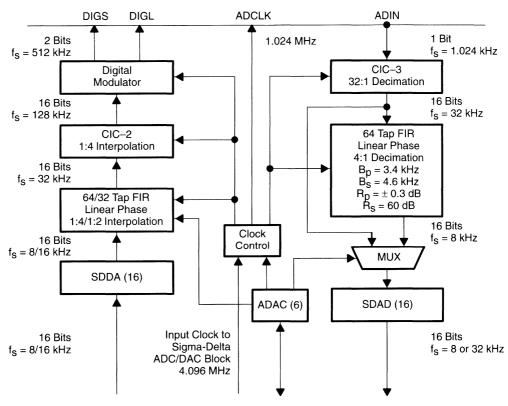

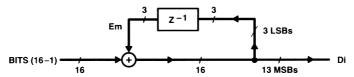

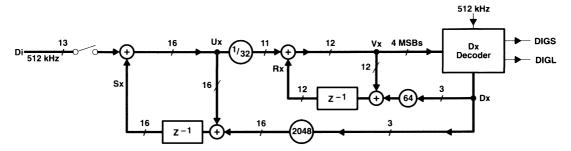

| 2–19 | Oversampling Digital Filters in the MSP58C80 2-42                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

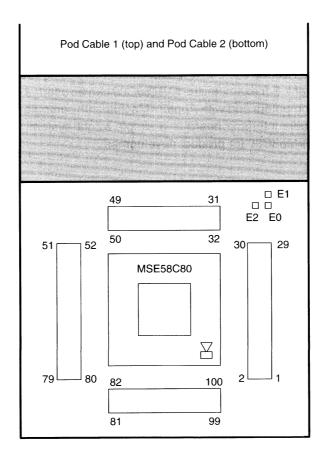

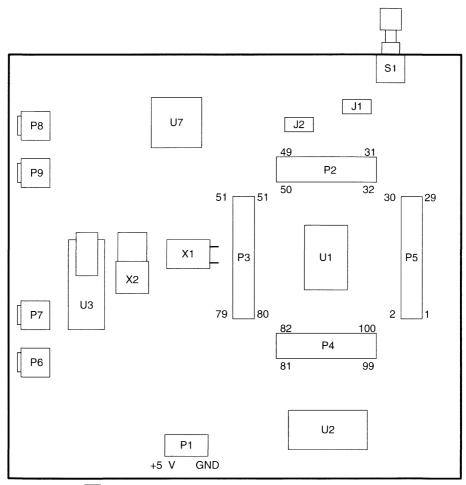

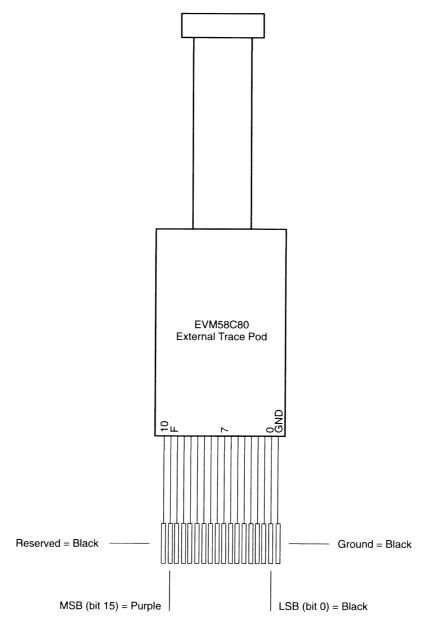

| 4–1  | EVM58C80 SE Pod 4-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

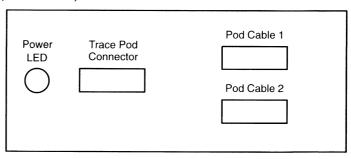

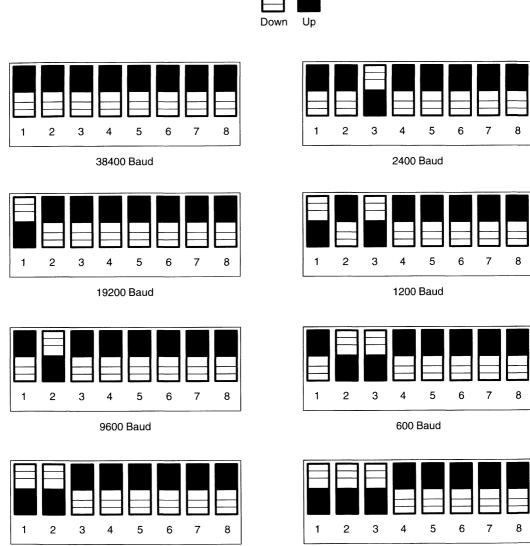

| 4–2  | EVM58C80 Box (Front View) 4-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 4–3  | EVM58C80 Box (Rear View) 4-4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

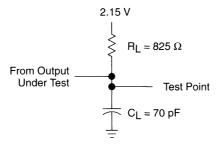

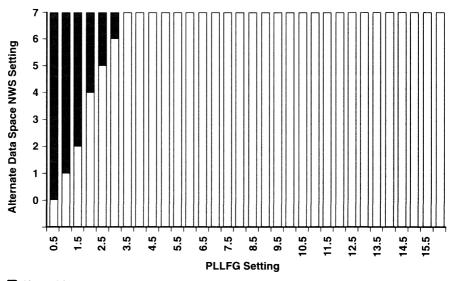

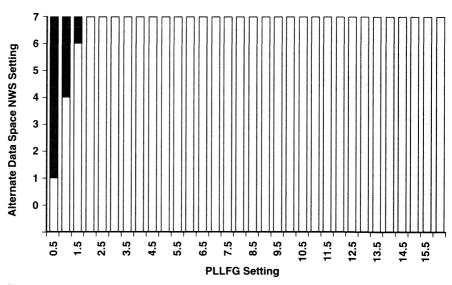

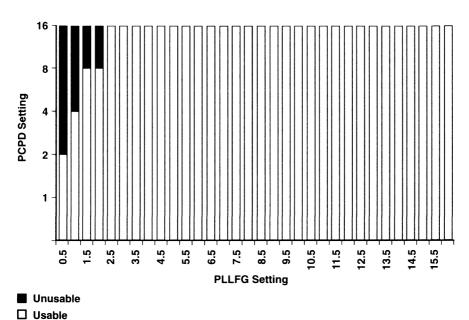

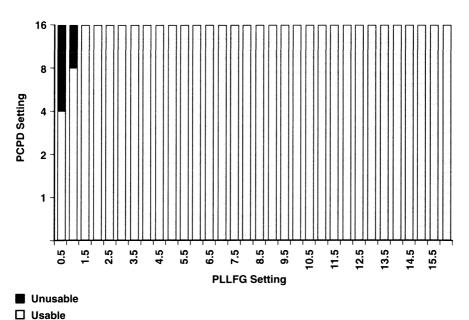

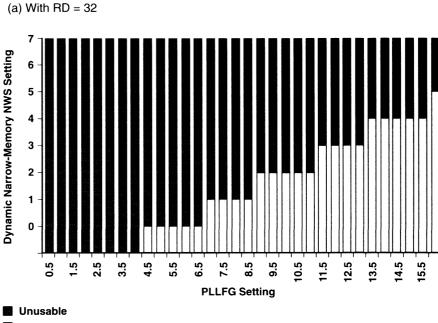

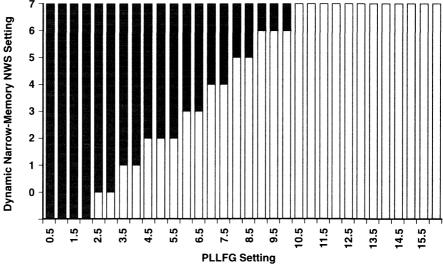

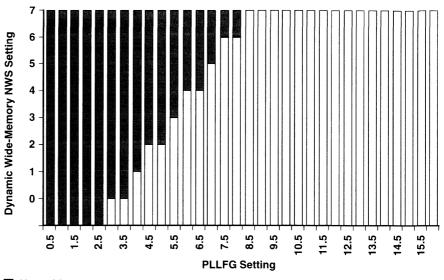

| 4–4  | AIB58C80                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |